## **Performance Characteristics:**

- Frequency band: 2~20GHz

- Noise factor: 2.5dB

- Gain: 15dB

- P1dB: +15dBm

- Self-biased power supply: +5V@65mA

- Input/Output :50ohm match

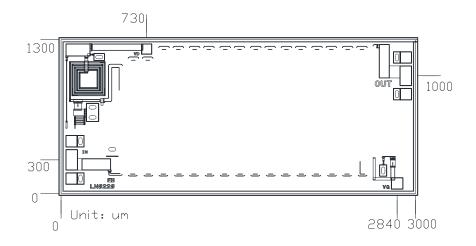

- Chip size: 3mm x 1.3mm x 0.1mm

## **Product Description :**

CW-LN362 is a GaAs MMIC low noise amplifier chip with a frequency range covering 2 to 20 GHZ and a noise factor of 2.5dB.

#### Typical Maximum Typical Maximum Typical Maximum Indicators Minimum Minimum Minimum Units value value value value value value 6~12 12~20 Frequency 2~6 GHz range 14.9 15 14.8 \_ Gain \_ \_ \_ dB \_ \_ ±0.2 ±0.2 ±0.2 Gain flatness \_ \_ dB 18 15 25 Input return loss \_ \_ \_ \_ dB Output return 18 15 20 dB \_ \_ \_ -\_ \_ loss Output power 1dB 15 14.5 14 dBm \_ \_ \_ -\_ \_ compression point 24.5 24 25 Output IP3 \_ \_ dBm \_ Saturated 16.5 16 \_ 17 \_ dBm 2.0 2.5 2.5 Noise factor dB \_ 65 65 Working current 65 \_ -\_ \_ \_ \_ mΑ

## Electrical parameters : (TA=25°C, VD=+5V, IDD=65mA)

| Use limiting parameters : |                     |             |  |

|---------------------------|---------------------|-------------|--|

|                           | Input power         | +15dBm      |  |

|                           | Storage temperature | -65°C~150°C |  |

|                           | Service temperature | -55℃~85℃    |  |

#### 1: .... U

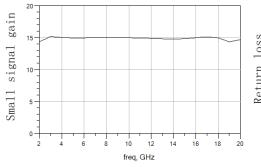

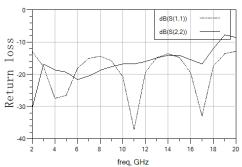

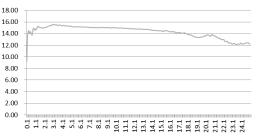

## Typical curve :

10.00

9.00

8.00

7.00

6.00

5.00

4.00

3.00

2.00

1.00 0.00

# Dimensional drawing : ( unit mm )

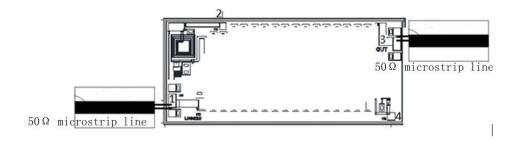

## Suggested assembly drawing:

## Pad Description: 3mil assembly clearance

| Pad number       | Function | Description                                                             |

|------------------|----------|-------------------------------------------------------------------------|

| 1                | IN       | The pad is AC coupled with a matching value of 500hm                    |

|                  |          | The pad provides the amplifier's power supply voltage and requires an   |

| 2                | VD       | external 100pF and 0.01uF bypass capacitor with the pad to 100pF        |

|                  |          | capacitor bonding wire controlled within 500um                          |

| 3                | OUT      | The pad is AC coupled and matches up to 500hm                           |

|                  |          | The pad can be adjusted chip gain, suspended during normal use, and can |

| 4                | VG       | be connected to 0-0.5V voltage if you need to increase the gain, or     |

|                  |          | -035-0V voltage if you need to decrease the gain                        |

| Back of the chip | GND      | The back of the chip must be connected to the RF/DC ground              |

#### Instructions:

Storage: The chip must be placed in a container with electrostatic protection and stored in a nitrogen environment.

**Cleaning treatment:** The bare chip must be operated and used in a purified environment. It is forbidden to use liquid cleaning agent to clean the chip.

**Electrostatic protection:** Strictly comply with the ESD protection requirements to avoid electrostatic damage to the components.

**General operation:** Use vacuum chuck or precision pointed tweezers to pick up the chip. Avoid touching the surface of the chip with tools or fingers during handling.

**Mounting operation:** The chip can be installed using AuSn solder eutectic welding or conductive adhesive bonding process. The mounting surface must be clean and flat.

**Bonding operation:** Input and output with 2 (recommended diameter of 25um gold wire) bonding wire, bonding wire length less than 250um is optimal. It is recommended to use the smallest possible ultrasonic energy. Bonding begins at the pressure point on the chip and ends at the package (or substrate).