## **Performance Characteristics**

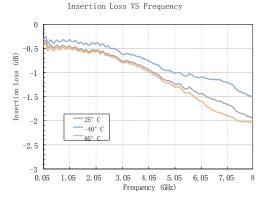

- Operating frequency band: 0.1GHz~6GHz

- Low insertion loss: 0.5dB @0.1GHz to 2GHz (typ)

- 0.9dB @2GHz to 4GHz(typ)

1.4dB @4GHz to 6GHz(typ)

- Attenuation range: 0.5dB~31.5dB

- Package Size: 24-pin QFN, 4mmx4mm

### summarize

The CWAT083SP4 is a six-bit numerically controlled attenuator with a frequency range of 0.1GHz to 6GHz and an insertion loss of less than 1.4dB typical. High attenuation accuracy, 0.5dB attenuation step, 3V bias voltage.

The CWAT083SP4 attenuator is available in a 24-pin, 4mmx4mm surface mount, leadless plastic package. The pin pads are coated with Sn or NiPdAu.

### Electrical performance table (TA=+25°C, VDD=3.3V)

| *This indicator is only the reference day<br>official mass production lot is 23dBm. | a for the engineering validation 1 | ot, and the | indicator for | the |

|-------------------------------------------------------------------------------------|------------------------------------|-------------|---------------|-----|

| Parameter name                                                     | working conditions                         | minimum<br>value | typical<br>value | maximum<br>values | unit (of<br>measure) |

|--------------------------------------------------------------------|--------------------------------------------|------------------|------------------|-------------------|----------------------|

| frequency range                                                    |                                            | 0.1              |                  | 6                 | GHz                  |

|                                                                    | 0.1GHz $^{2}$ GHz                          |                  | 0.5              | 0.8               | dB                   |

| insertion loss                                                     | $2 \mathrm{GHz}^{\sim} 4 \mathrm{GHz}$     |                  | 0.8              | 1.3               | dB                   |

|                                                                    | 4GHz~6GHz                                  |                  | 1.3              | 1.8               | dB                   |

| Attenuation range                                                  | $0.\ 2 \mathrm{GHz}^{\sim} \mathrm{6 GHz}$ | 0.5              |                  | 31.5              | dB                   |

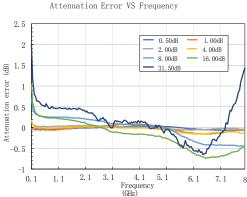

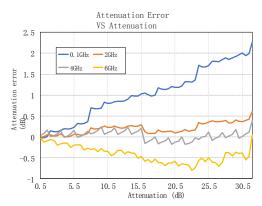

| Attenuation accuracy                                               | $0.2 \mathrm{GHz}^{\sim} \mathrm{6GHz}$    | -0.5             |                  | 1                 | dB                   |

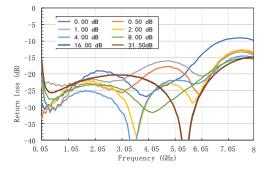

| Input and output return loss                                       |                                            |                  | 20               |                   | dB                   |

| Bias Voltage (VDD)                                                 |                                            | 3                | 3.15             | 3. 3              | V                    |

| Bias Current (IDD)                                                 |                                            |                  |                  | 1                 | mA                   |

| 0.1dB compression point input power<br>(P0.1dB)                    |                                            |                  | 21               |                   | dBm                  |

| Input third-order intercept point                                  |                                            |                  | TBD              |                   | dBm                  |

| Switching time (insertion loss state to maximum attenuation state) | 10% to 90% RF output                       |                  | 240              |                   | ns                   |

| Switching time (maximum attenuation state to insertion loss state) | 10% to 90% RF output                       |                  | 100              |                   | ns                   |

| switching time                                                     | 50% Vctl to 10%/90% RF output              |                  | 300              |                   | ns                   |

| Recommended Input Power                                            |                                            |                  |                  | 20*               | dBm                  |

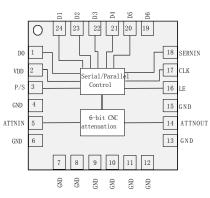

## functional block diagram

## typical application

- Mobile infrastructure

- satellite communications

- microwave

V0.62307

Instrumentation

6.05

7.05 8

### Six-position digitally controlled attenuator

Input Return Loss VS Frequency

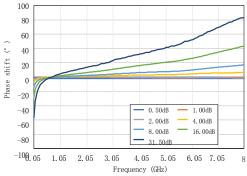

0. 50dB 2. 00dB

8. 00dB

31. 50dB

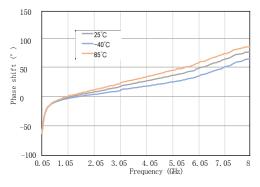

test curve

V0.6 2307

CWAT Digital Attenuator Series

€ -20 loss -25 -30 Return -35 -40 0.05 1.05 2.05 3.05 4.05 5.05 8 Frequency (GHz) Phase Shift VS Frequency

0dB

1. 00dB

4. 00dB

16. 00dB

0

-5

-10

-15

Six-position digitally controlled attenuator

V0.6 2307

#### test curve

#### **Operating parameters**

| Bias voltage <b>VDD</b> | 3V to 3.3V                            |

|-------------------------|---------------------------------------|

| Control voltage VCTL    | 0V to 0.3V (Low)<br>3V to 3.3V (High) |

| operating temperature   | -40°C∼+85°C                           |

Control Port: D0~D5, P/S, LE, CLK, SERNIN

#### Absolute maximum rating

| RF Input Power       | +22dBm*         |

|----------------------|-----------------|

| Bias Voltage VDD     | -0.3V~3.6V      |

| Control Voltage VCTL | -0.5 V~VDD+0.3V |

| Storage temperature  | -65°C∼+150°C    |

\*This indicator is only the reference data for the engineering validation lot, and the indicator for the official mass production lot is 26dBm.

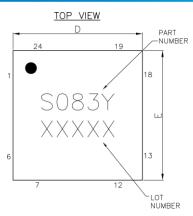

#### **Package Information**

| model number | package material         | Pad plating  | MSL rating [1] | Package<br>identification | environmental<br>requirement |

|--------------|--------------------------|--------------|----------------|---------------------------|------------------------------|

| CWAT083SP4   | Green resin<br>compounds | Sn or NiPdAu | MSL 3          | S083<br>XXXXX             | RoHS compliant               |

[1] Maximum reflow temperature 260° C

[2] XXXXX is the lot number

SIDE VIEW

2. Lead frame material: copper alloy

3. Package surface warpage: not more than 0.05mm 4. All ground pins should be connected to PCB RF

Description: 1. Unit: mm

A2

A1

SEATING PLANE

С

V0.6 2307

| Dimension Table (unit:mm) |                |         |      |  |

|---------------------------|----------------|---------|------|--|

| Symbol                    | MIN            | NOM     | MAX  |  |

| Α                         | 0.70           | 0.75    | 0.80 |  |

| A1                        | 0.00           |         | 0.05 |  |

| A2                        |                | 0.20Ref |      |  |

| b                         | 0.20 0.25 0.30 |         |      |  |

| D                         | 3.90           | 4.00    | 4.10 |  |

| D2                        | 2.60           | 2.70    | 2.80 |  |

| е                         | 0.50BSC        |         |      |  |

| Ne                        | 2.50BSC        |         |      |  |

| Nd                        |                | 2.50BSC |      |  |

| E                         | 3.90           | 4.00    | 4.10 |  |

| E2                        | 2.60           | 2.70    | 2.80 |  |

| К                         | 0.20           |         |      |  |

| L                         | 0.30           | 0.40    | 0.50 |  |

| aaa                       | 0.08           |         |      |  |

### **Pin Definitions**

ground.

| Pin Number | functional symbol | Functional Description                  | Pin Number | functional symbol | Functional Description                |

|------------|-------------------|-----------------------------------------|------------|-------------------|---------------------------------------|

| 1          | DO                | Console 0 port                          | 13         | GND               | radio-frequency zone                  |

| 2          | VDD               | DC Bias                                 | 14         | ATTNOUT           | RF Output, no isolation<br>capacitors |

| 3          | P/S               | serial-to-parallel<br>selector terminal | 15         | GND               | radio-frequency zone                  |

| 4          | GND               | radio-frequency zone                    | 16         | LE                | enabling terminal                     |

| 5          | ATTNIN            | RF Input, No Barrier<br>Capacitors      | 17         | CLK               | clock side                            |

| 6          | GND               | radio-frequency zone                    | 18         | SERNIN            | Serial Data Input                     |

| 7          | GND               | radio-frequency zone                    | 19         | D6                | let sth. lie idle                     |

| 8          | GND               | radio-frequency zone                    | 20         | D5                | Console 5 ports                       |

| 9          | GND               | radio-frequency zone                    | 21         | D4                | Console 4 ports                       |

| 10         | GND               | radio-frequency zone                    | 22         | D3                | Console 3 ports                       |

| 11         | GND               | radio-frequency zone                    | 23         | D2                | Console 2 ports                       |

| 12         | GND               | radio-frequency zone                    | 24         | D1                | Console 1 port                        |

Six-position digitally controlled attenuator

V0.6 2307

#### truth table

|      | Control Port Status |      |      |      |      | Attenuation status (dB) |

|------|---------------------|------|------|------|------|-------------------------|

| D5   | D4                  | D3   | D2   | D1   | D0   | Attenuation status (ub) |

| Low  | Low                 | Low  | Low  | Low  | Low  | zero state (math.)      |

| Low  | Low                 | Low  | Low  | Low  | High | 0.5                     |

| Low  | Low                 | Low  | Low  | High | Low  | 1.0                     |

| Low  | Low                 | Low  | High | Low  | Low  | 2.0                     |

| Low  | Low                 | High | Low  | Low  | Low  | 4.0                     |

| Low  | High                | Low  | Low  | Low  | Low  | 8.0                     |

| High | Low                 | Low  | Low  | Low  | Low  | 16.0                    |

| High | High                | High | High | High | High | 31.5                    |

Any combination of the above states will provide attenuation approximately equal to the sum of the selected bits

### **Control mode selection**

| P/S status | control mode                                                |

|------------|-------------------------------------------------------------|

| Low        | side by side (of two processes, developments, thoughts etc) |

| High       | confuse two lines                                           |

The P/S pin must remain in a valid logic state (High or Low) and must not be left floating

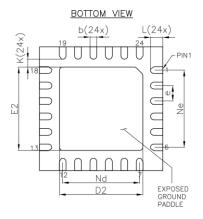

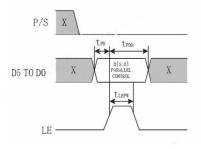

#### Serial control output

The serial control interface is active when the P/S pin is set high.

In serial mode, the six-bit serial data is first clocked to the highest bit when the CLK edge rises to the shift register, and then LE must be switched high to latch the new attenuation state. LE must be set low to write a set of six bits to the shift register, as CLK is masked to prevent the attenuation value from changing while LE remains high.

During serial mode operation, the serial control inputs (LE, CLK, SERNIN) and parallel control inputs (D0 through D5) must be maintained at valid logic levels (High or Low) at all times and must not be left floating. If the device driving these input lines experiences high impedance during sleep, it is recommended that the parallel control inputs be connected to ground and that pull-down resistors be used on all serial control input lines.

#### **RF Input and Output**

The attenuator is bi-directional; the ATTNIN and ATTNOUT pins are interchangeable as RF input and output ports. The attenuator is internally matched to  $50\Omega$  on the input and output; therefore, no external matching is required. The RF pins are DC coupled; therefore, DC blocking capacitors are required on the RF lines.

V0.6 2307

Six-position digitally controlled attenuator

Control mode selection

#### Parallel control output

The parallel control port has six digital control inputs (D5 through D0) for setting the attenuation value.D5 is the highest valid bit for selecting 16 dB attenuation and D0 is the lowest valid bit for selecting 0.5 dB attenuation.

During parallel mode operation, the serial control inputs (LE, CLK, SERNIN) and parallel control inputs (D0 through D5) must always be maintained at a valid logic level (High or Low) and must not be left floating. If the devices driving these input lines have high impedance during sleep, it is recommended that the serial control inputs be connected to ground and that pull-down resistors be used on all parallel control input lines.

Parallel mode is enabled by setting P/S low. There are two modes of parallel operation: direct parallel mode and latching parallel mode.

#### **Direct parallelism**

For direct parallel mode, LE must be held high. The attenuation state is changed directly using the control voltage inputs (D0 through D5). This mode is ideal for manually controlling the attenuator and using hardware, switches or jumpers.

#### Latch Parallel Mode

When changing the control voltage inputs (D0 through D5) to set the attenuation state, the LE port must be held low. To set the desired state, LE must be switched high to transfer 7-bit data to the attenuator array bypass switch and then low to latch the change into the device.

Latch Parallel Mode Timing Diagram

### Power-up sequence and status

- 1. GND is energized.

- 2. VDD energized.

- 3. Turn on the digital control inputs (the relative order of the digital control inputs is not important).

- 4. Turn on the RF input.

- 5. For latched parallel mode, the LE must be switched. the relative order of the digital inputs does not matter as long as the inputs are energized after ground and VDD.

When energized, the logical state of the unit is maximum attenuation when LE is set to low. The attenuator locks at the desired energized state after approximately 200ms of energization.

### E-mail:sales@cdcwtec.com Website: www.cdcwtec.com

Chengdu Cuiwei Electronic Co.,LTD

CWA

Six-position digitally controlled attenuator

V0.6 2307

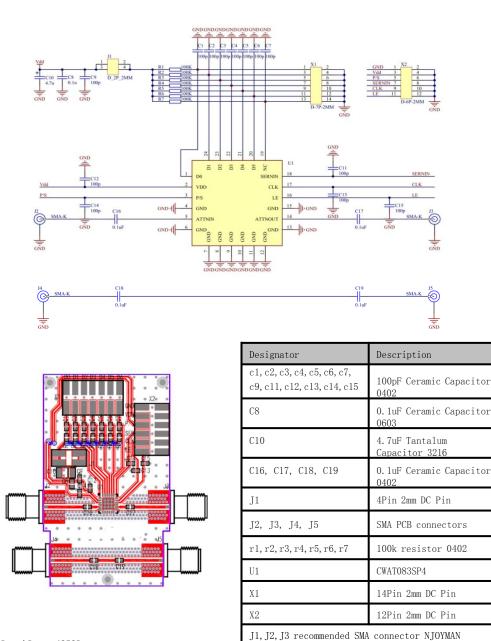

evaluation board

CWAT

Circuit Board:Rogers4350B

Device application board should be designed in accordance with the design of RF circuits, signal lines according to the 50  $\Omega$  impedance design, while the package shell of the ground pin near the ground (similar to the figure), connecting the top and bottom grounding surface should be sufficiently many grounding holes.

D550B12E01-048

V0.62307

Six-position digitally controlled attenuator

| SPEC              |

|-------------------|

| 12.00 +/-0.30     |

| Ø1.50 +0.10/-0.00 |

| 4.00 +/-0.10      |

| 1.75 +/-0.10      |

| Ø1.50 MIN         |

| 4.30 +/-0.10      |

| 4.30 +/-0.10      |

| 8.00 +/-0.10      |

| 2.00 +/-0.10      |

| 1.10 +/-0.10      |

| 0.30 +/-0.05      |

| 5.50 +/-0.05      |

|                   |

#### caveat

- 1. Attempts to clean the chip surface with wet chemical methods are prohibited.

- 2. This product is a static sensitive device, storage and use of attention to anti-static.

- 3. Store in a dry environment.

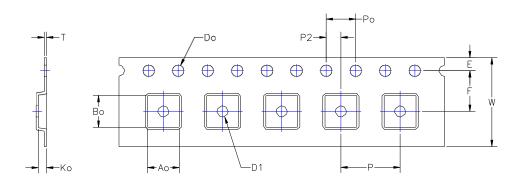

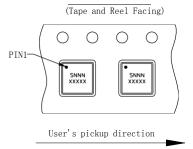

Orientation of components in the carrier tape

Description:

- 1. Unit: mm

- 2. Material: anti-static polypropylene

- 3. Color: black

- 4.10 positioning hole center distance (PO) cumulative tolerance  $\pm$  0.2