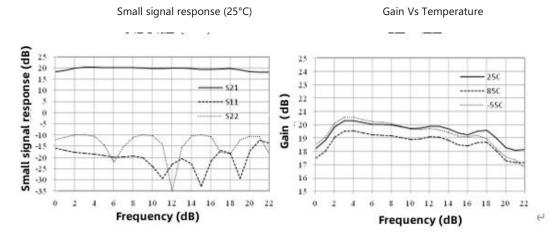

### **Performance characteristics:**

- Frequency band:DC~20GHz

- Noise factor:1.5dB

- Gain: 20dB

- Input and output return loss: >17dB/>10dB

- Output P1dB:19dBm

- Output IP3:33dBm

- Power supply:+8V@118mA

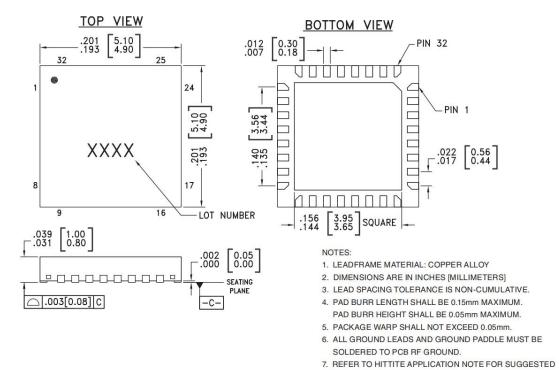

- 32 Lead 5x5 mm QFN Package: 25 mm<sup>2</sup>

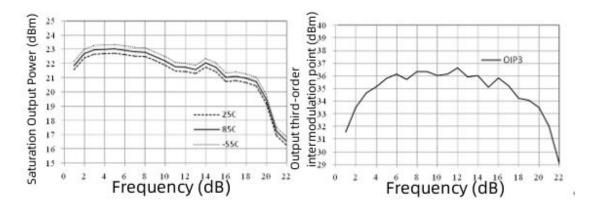

#### ACG2 N/C N/C N/C N/C 28 27 26 30 29 23 N/C Vgg2 2 N/C 3 22 N/C N/C 4 21 RFOUT & Vdd 5 20 N/C 19 N/C N/C 6 N/C 7 18 N/C N/C 8 17 N/C

Functional Diagram

### **Product Description:**

The CW-LN465SP5 is a GaAs MMIC ultra wideband low-noise amplifier chip with a frequency range covering DC~20GHz and a typical noise figure of 1.5dB throughout the band. the CW-LN465SP5 is powered by +8V.

### **Electrical parameters:**( $T_A=25^{\circ}C$ , VD=+8V, VG=-0.25V)

| Indicators         | Minimum value | Typical values | Maximum value | Unit |

|--------------------|---------------|----------------|---------------|------|

| Frequency range    | DC~20         |                |               | GHz  |

| Noise factor       | 1.2           | 1.5            | 3.2           | dB   |

| Gain               | 18.2          | 20             | 20.2          | dB   |

| Input Return Loss  | 17            | -              | -             | dB   |

| Output Return Loss | 10            | -              | -             | dB   |

# **Usage limitation parameters:** (Exceeding any of the above maximum limits may result in permanent damage.)

| Input power           | +23dBm    |  |

|-----------------------|-----------|--|

| Control voltage       | +9V       |  |

| Storage temperature   | -65℃~150℃ |  |

| Operating temperature | -55℃~125℃ |  |

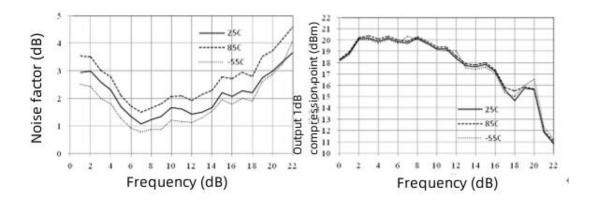

### **Typical curves:**

Output saturation power Vs Temperature

### Output third-order intermodulation point (25°C)

## PIN Description

| Pin Number                                                 | Function       | Description                                                                                                                              | Interface Schematic       |  |

|------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|

| 1, 3, 4, 6 - 12, 14,<br>17, 18, 19, 20,<br>22 - 28, 31, 32 | N/C            | The pins are not connected internally; however, all data shown herein was measured with these pins connected to RF/DC ground externally. |                           |  |

| 2                                                          | Vgg2           | Gate Control 2 for amplifier. +1.5V should be applied to Vgg2 for nominal operation.                                                     | Vgg2                      |  |

| 5                                                          | RFIN           | This pad is DC coupled and matched to 50 Ohms.                                                                                           | RFIN O                    |  |

| 13                                                         | Vgg1           | Gate Control 1 for amplifier.                                                                                                            | Vgg10                     |  |

| 15                                                         | ACG4           |                                                                                                                                          | RFIN ACG4                 |  |

| 16                                                         | ACG3           | Low frequency termination. Attach bypass capacitor per application circuit herein.                                                       |                           |  |

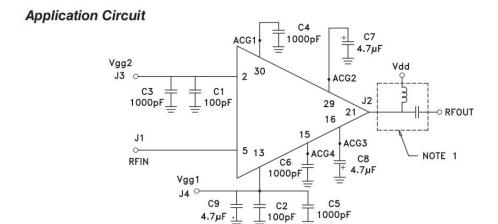

| 21                                                         | RFOUT &<br>Vdd | RF output for amplifier. Connect the DC bias (Vdd) network to provide drain current (Idd). See application circuit herein.               | ACG1 O-VV RFOUT & Vdd Vdd |  |

| 29                                                         | ACG2           | Low frequency termination. Attach bypass capacitor per                                                                                   |                           |  |

| 30                                                         | ACG1           | application circuit herein.                                                                                                              | = '                       |  |

| Ground Paddle                                              | GND            | Ground paddle must be connected to RF/DC ground.                                                                                         | GND                       |  |

### Outline drawing: (unit mm)

LAND PATTERN.

NOTE 1: Drain Bias (Vdd) must be applied through a broadband bias tee or external bias network.